芯片的未来发展方向在哪里?

2009 年,芯片行业知道自己遇到了问题。时任台积电研发主管的蒋尚义认为他有一个解决方案。

他向他的老板、台积电创始人张忠谋建议,他们应该探索芯片制造过程中不太先进的部分,即芯片封装,而不是把更多的晶体管挤到越来越小的芯片上,这是使它们变得更强大的传统方法。

蒋尚义说“我告诉张主席,由于摩尔定律在未来几年可能会放缓,我们可能想尝试其他可以继续提高芯片计算性能的方法。”

英特尔联合创始人戈登·摩尔 (Gordon Moore) 于 1965 年首次提出摩尔定律,该定律认为芯片上的晶体管数量每年大约会增加一倍,随着时间的推移,计算机芯片的功能将呈指数级增长。1975年修订为每两年一次。

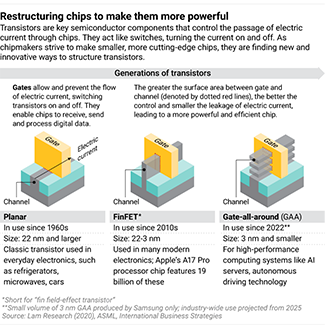

第一批晶体管是控制芯片电流的重要元件,长度为一厘米,但到了 20 世纪 50 年代,它们的测量单位为毫米。如今,业界以纳米为单位进行讨论——人类 DNA 链的直径为2.5 纳米。现在单个芯片拥有数十亿个晶体管。

摩尔定律塑造了芯片行业数十年的发展轨迹,其在小型化方面的进步推动了从个人电脑到智能手机再到人工智能的整个行业。即使边际效率的提高也可以在计算任务的复杂性方面带来巨大的收益。例如,大多数专家认为,仍处于起步阶段的生成人工智能领域需要的计算能力只能使用 4 纳米或更小的芯片才能实现。

在台积电运营的像这样的先进芯片工厂中,世界各地的芯片制造商都在努力使半导体变得更小。(台积电供图)

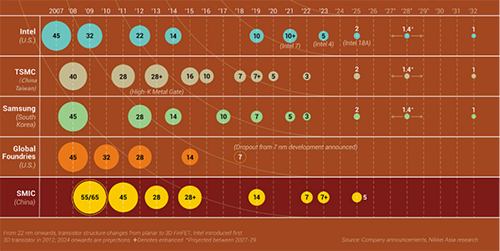

为了制造更小、更快的芯片,台积电、美国英特尔和韩国三星等少数公司每年花费数十亿美元,将摩尔定律推向极限。通过这样做,他们对竞争对手取得了巨大的领先优势,形成了一个本质上是两级的行业,顶尖的厂商竞相在 2025 年生产 2 纳米芯片。

但是,晶体管的缩小程度以及指甲盖大小的芯片中可以封装多少个晶体管是否存在极限?与业内许多人一样,蒋尚义长期以来一直担心摩尔定律的最终终结。

蒋尚义说“如果摩尔定律真的达到极限,将会给半导体行业带来巨大的影响。”

台积电前研发主管蒋尚义认为,更好的计算机系统集成可能是芯片制造商抵抗摩尔定律放缓的一种方式。

“如果没有新的解决方案,芯片行业最终可能会在20年后成为一个传统行业,而不是现在的高科技行业,”他补充道。

芯片是否会像钢铁和塑料行业一样完全商品化仍然是一个有争议的问题,但蒋尚义在 2009 年观察到的摩尔定律的放缓已经对该行业和地缘政治产生了深远的影响。

这种放缓可能会给那些在[芯片]竞赛中落后的国家,比如中国,提供迎头赶上的机会。

追赶

已有迹象表明,蒋尚义的预测正在成为现实,而最大的证据之一就是领先者和落后者之间的差距正在缩小。

“要跑得比团队中跑得最快的人更快是很困难的。但一旦最快的企业无法跑得更快……那么其他企业就会赶上它,”行业资深人士、加拿大研究公司 TechInsights 的副主席丹·哈奇森 (Dan Hutcheson) 说道。“在竞赛中,领先者不能绊倒,哪怕一次。”

根据《日经亚洲》的分析,英特尔与中国最大芯片制造商之间的技术差距比以往任何时候都小。

英特尔位于马来西亚的芯片封装工厂的一名经理穿着防护装备,以防止洁净室受到污染。(照片由英特尔提供)

虽然这在一定程度上是由于中国决心在美国出口限制的情况下提高其芯片能力,但这也是人们长期以来担心行业领跑者尖端创新放缓的结果。

美国巨头英特尔曾经比中国竞争对手至少领先四五年,相当于芯片制造领域的两代以上。现在它的领先优势大约是三年,或者说是一代半。

今年,华为新款 Mate 60 Pro 智能手机采用中芯国际 7 纳米芯片,这是中国在与美国的科技战中向前迈出的重要一步(盖蒂图片社摄影)

台积电和三星现在正在生产 3 纳米芯片,而英特尔则处于 5 纳米阶段。这三家公司都在竞相到 2025 年生产 2 纳米芯片。

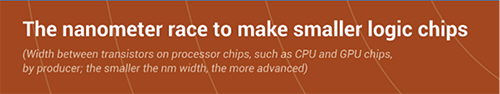

从技术上讲,纳米是指晶体管栅极的宽度(见下图) 。较小的栅极允许将更多晶体管挤入同一区域,从而实现更强大的处理器。

但门的尺寸是有限度的,不久之后进一步缩小将是不可能的。因此,公司提出了新的芯片架构,并开始使用看似违反物理原理的新材料。

早在 2012 年,英特尔就率先将其晶体管从大多数传统芯片中广泛使用的二维结构转变为 3D 结构,即 FinFET。台积电和三星很快也纷纷效仿。

现在,芯片巨头正在寻找一种更复杂的晶体管结构——所谓的全环栅——以将更多的计算能力压缩到同一个微小的表面积上。但像这样的创新正变得越来越昂贵。

台积电、英特尔和三星电子到 2022 年的资本支出合计将超过 970 亿美元,是欧盟计划在未来十年推动欧盟芯片产业支出的两倍多。

美国芯片咨询公司 International Business Strategies 的行业资深人士兼首席执行官汉德尔·琼斯 (Handel Jones) 告诉《日经亚洲》:“成本结构正在减缓发展速度。过去台积电每两年做一次新技术,现在是三年,未来可能会更长。”

行业高管和分析师一致认为:摩尔定律步伐的放缓,为落后企业提供了千载难逢的机会,缩小与全球领先企业的差距。

顶级工程研究机构中国工程院吴汉明表示:“后摩尔定律时代,芯片性能增长放缓,业界正在寻找新的技术方向,进一步加速芯片性能。

“对于多年来一直处于追赶状态的中国来说,这是一个很好的机会。”

一个新的竞争环境

早在 2009 年,台积电就开始认真探索芯片小型化的替代方案,蒋尚义建议封装可能是提高性能的替代方法。

芯片封装一度被视为业界的事后想法,仅仅是保护集成电路的一种方式。与芯片制造相比,它对技术的要求要低得多,而且似乎并没有像增加晶体管数量那样提供同样的性能改进。

但蒋意识到,以新颖的方式连接不同类型的芯片(例如内存和处理器)可以带来巨大的改进。2009 年,他说服台积电创始人张先生支持他的封装计划,并获得了 1 亿美元的预算和 400 人的团队来使其发挥作用。

现年 92 岁的台积电创始人张忠谋在 2009 年批准了该公司的第一个大型芯片封装项目。(Ken Kobayashi 摄)

成功并没有立即到来。

蒋尚义回忆道,头两年,没有芯片客户愿意尝试新技术,因为与传统封装相比,它太贵了。“一些台积电高管甚至嘲笑我,说我的提议变成了每月只生产 50 片晶圆的业务。”

现在很少有人笑了。

芯片封装现已被公认为全球顶级芯片制造商的最新战场。

今年,英特尔 40 年来首次重新设计了其旗舰 PC 芯片组的架构,以利用先进的封装技术。负责中央处理、人工智能计算、图形和数据传输接口的四个“模块”已被组合成一个芯片。

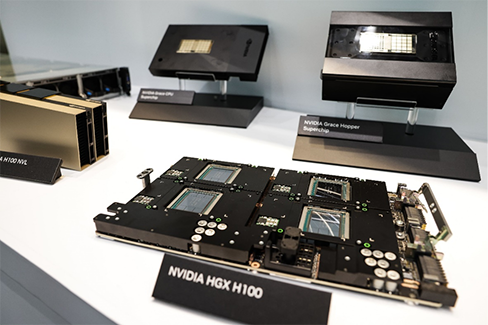

Nvidia 的 H100 芯片组是 OpenAI 广受欢迎的 ChatGPT 背后的动力源泉,集中体现了 这一趋势。其集成设计将图形处理器与六颗高带宽内存芯片直接连接,并采用台积电提供的先进封装技术。

H100芯片组由美国Nvidia在台积电的帮助下生产。(盖蒂图片社拍摄)

2021年,英特尔和台积电等行业巨头开始了有史以来最大规模的芯片封装扩张,承诺对该技术进行总计超过200亿美元的多年投资。就连美国政府也开始关注,除了 520 亿美元的半导体补贴之外,还额外拨款 30 亿美元用于芯片封装的研究。

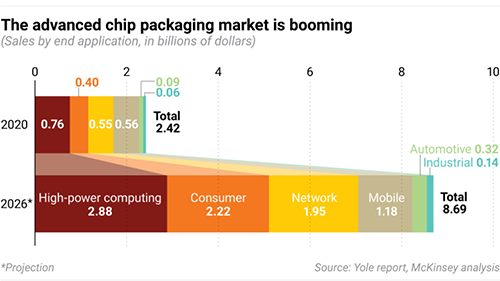

据研究机构 IDC 估计,新型芯片封装市场预计将从今年的 437 亿美元增至 2028 年的 743 亿美元。

先进芯片封装市场(涉及将多个芯片堆叠到晶圆上)的市场增长尤其迅速。

欧洲领先芯片制造商恩智浦半导体公司的首席技术官 Lars Reger 告诉《日经亚洲》,在数字计算领域,“封装”可能会接管许多创新。他说:“让我们像煎饼一样堆叠所有这些芯片,然后进行三维......堆叠一个 5 nm 芯片,再在上面堆叠另一个,然后将其制成一个封装。”

中国有机会吗?

在中国,由于美国制裁切断了中国芯片制造商获得先进芯片机器的渠道,芯片制造商正在努力应对摩尔定律进一步放缓的问题。

一般来说,由于芯片封装对技术的要求低于制造,因此进入和进步的壁垒较低。

“先进封装不需要非常精密、复杂的设备,并且可以使用先进封装技术将[性能]从7纳米推进到5纳米甚至3纳米,”景硕互联科技的一位高管Nvidia 和 AMD 芯片基板供应商说道。“因此在某种程度上,摩尔定律的放缓对于中国芯片制造商来说是缩小与领跑者差距的好时机。”

芯片设施建设商诺瓦科技(Nova Technology)总裁马大卫(David Ma)表示,芯片封装的出现对中国来说是一个潜在的福音。“如果未来先进芯片封装成为主旋律,当然,这可能为中国提供另一个捷径,”他说。

业内人士表示,中国芯片行业可以利用芯片封装热潮赶上其他全球半导体领导者。(盖蒂图片社拍摄)

体力有限,食欲无限

对于物理定律多久会终结晶体管越来越小,目前还没有定论。

台积电董事长刘德音在 9 月份的一次行业活动中表示:过去 50 年来,半导体技术的发展就像走在隧道里一样。前方的道路是清晰的,并且有一条明确的道路。每个人都知道需要做什么:缩小晶体管。

“现在,我们已经到达了这条隧道的出口。半导体技术的开发变得越来越困难。然而,在隧道之外,还有更多的可能性......我们不再发现自己受到隧道的限制。”

目前还没有人敢完全放弃摩尔定律。

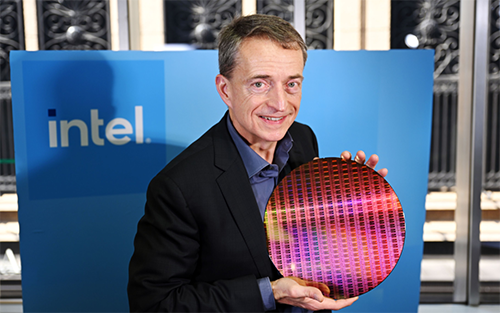

英特尔首席执行官帕特·基辛格(Pat Gelsinger)誓言要“耗尽元素周期表”,以保持摩尔定律的生命力,该公司试图在四年内推进五代产品,以夺回在半导体制造领域失去的领先地位。基辛格上个月在台北表示:“我们将改变物理学并寻找新的创新方法——包括晶体管架构以及我们在这里的封装和交付方式。”

除了两年内预计推出的 2 纳米芯片之外,领先制造商已经在开发 1.4 纳米芯片,并计划在 2032 年推出 1 纳米芯片。

英特尔首席执行官帕特·基辛格(Pat Gelsinger)承诺在其使命中“改变物理学”,创造更强大的芯片。

这需要比利时领先的研究机构 IMEC 在 2022 年推出一种新的晶体管结构。英特尔高级副总裁Sanjay Natarajan表示,该公司在垂直堆叠新品种晶体管方面取得了早期成功,取得了关键突破,为生产小于1纳米的芯片铺平了道路。

“十年前,考虑 3 纳米芯片几乎是不可想象的。但现在(它们)已经投入生产,”美国芯片材料制造商 Entegris 首席技术官 James O'Neill 说道。

全球最大的芯片设备制造商 ASML 的机器定义了集成电路的印刷尺寸,该公司表示,“摩尔定律已多次被宣布失效,但它仍然存在。”

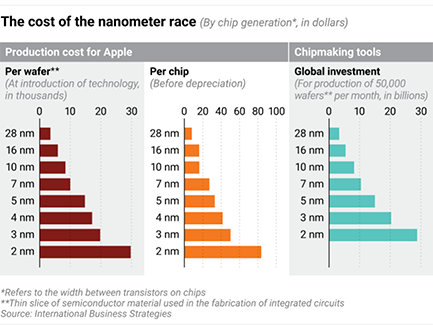

然而,雄心壮志必须根据成本来衡量。据 International Business Strategies 称,建造适合运行人工智能计算的 2 纳米芯片的初始投资将接近 300 亿美元,是为消费电子产品建立微控制器芯片工厂的 10 倍。

“我们在1nm之后不断突破的目的是什么?”日本一家领先的芯片生产设备制造商的高管想知道。“我们只是追求技术突破吗?我们必须考虑什么才能证明如此大量的资源和投资是合理的。”

对于像苹果这样在产品中使用尖端芯片的公司来说,生产成本已经飙升。例如,制造 iPhone 处理器的成本在过去十年中增加了十倍。

麦肯锡公司高级合伙人 Ondrej Bur kacky 表示:“每个晶体管成本下降的逻辑基本上在 28 nm 时代就结束了。”他补充说,尖端芯片将变得越来越难以负担,而且进步必须使对客户的经济意义。

台积电的刘德音说“我不认为所有的芯片制造商都会到达最后的终点线。当今推动半导体技术发展的途径有很多。”

芯片巨头台积电正在美国亚利桑那州建设一座大型工厂,计划于 2025 年开业。(郑廷芳摄)

然而,芯片行业的一些声音认为黄金时代可能已经结束。“尖端技术有一天会成为成熟技术,这是不可避免的。”日本领先的芯片工具供应商之一佳能的一位行业资深人士这样认为,许多行业都发生过这种情况,例如显示器行业,而且将来也可能发生在芯片行业。

“虽然处理器性能仍在提高,但每一代的增长率都在下降。......我们需要对这些后续技术(半导体物理之外)进行数十或数百倍的投资,因为计算机的改进对经济非常重要,”麻省理工学院计算机科学未来科技研究项目主任尼尔·汤普森和人工智能实验室说道。

奥地利领先芯片基板供应商 AT&S 首席技术官 Peter Griehsnig 表示,量子计算机仍然是一项新兴技术,可能是未来的选择之一。“如果你将服务器与量子计算机集成以实现特定算法,这将是一个显著提高性能的机会。

台积电前研发主管蒋尚义认为未来实现更快计算的途径很可能是半导体以外的技术。他表示,展望未来,理想的情况将是“完全不同的东西,可以取代硅芯片,并可以继续提高计算性能。业界仍在探索所有可能性,但还没有明确的答案。”

内容质量低

不看此公众号

文章来源:半导体产业纵横编译自日经亚洲

联系人:袁经理

手机:051683539599

电话:051683539599

邮箱:ziyu.yuan@ae-fab.com

地址: 徐高新康宁路1号高科金汇大厦A座14楼