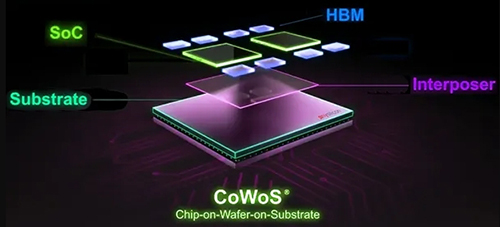

芯片封装由 2D 向 3D 发展的过程中,衍生出多种不同的封装技术。其中,2.5D 封装是一种先进的异构芯片封装,可以实现从成本、性能到可靠性的完美平衡。

目前 CoWoS 封装技术已经成为了众多国际算力芯片厂商的首选,是高端性能芯片封装的主流方案之一,英伟达算力芯片的需求增长大幅提升了 CoWoS 的封装需求,CoWoS 有望进一步带动先进封装加速发展。

CoWoS 技术是高端性能封装的主流方案

近年来,在先进封装飞速发展的背景下,开发相关技术的公司都将自己的技术独立命名注册商标,如台积电的 lnFO、CoWoS,日月光的 FoCoS,Amkor 的 SLIM、SWIFT,三星的 I-Cube、H-Cube 以及 Intel 的 Foveros、EMIB 等。台积电的 CoWos 技术是高端性能封装的主流方案之一。随着 2.5D 和 3D 封装解决方案变得越来越复杂,先进封装主要参与者的封装组合也在增加。根据 Yole《High End Performance Packaging 2022》,高端性能封装平台包括例如超高密度扇出型封装(UHD FO)、嵌入式硅桥(Embedded Si Bridge)、硅中介层(Si Interposer)、三维堆栈内存(3D Stack Memory)以及 3D SoC 技术。嵌入式硅桥有两种解决方案:LSI(台积电)和 EMIB(英特尔)。硅中介层技术包括台积电的 CoWoS、三星的 X-Cube以及英特尔的 Foveros 等解决方案。EMIB 与 Foveros 的结合产生了 CoEMIB 技术,主要应用于英特尔的 Ponte Vecchio 平台。三维堆栈内存分为三类,分别为 HBM、3DS 和 3D NAND 堆栈。

CoWoS 封装的优势

CoWoS(Chip on Wafer on Substrate)封装技术具有多项显著优势,这些优势使其在高性能计算和先进半导体制造领域中极为重要:

高密度集成:CoWoS技术允许在单一封装中集成多个芯片,包括处理器、内存和其他功能模块,实现高密度的系统集成。这种集成方式可以显著减少芯片间的物理距离,提高整体系统的性能。

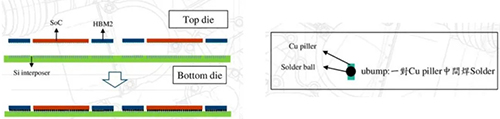

缩短互连长度:通过使用硅通孔(TSV)技术,CoWoS能够实现芯片间的垂直互连,从而大幅缩短信号传输路径,减少信号延迟和功耗。

增强信号完整性:由于互连长度的缩短,信号在传输过程中的衰减和干扰减少,从而提高了信号的完整性和可靠性。

降低功耗:更短的互连路径和优化的电源分布网络有助于降低整体功耗,这对于移动设备和数据中心等对能效有严格要求的应用尤为重要。

提高带宽和吞吐量:CoWoS技术支持高带宽内存(HBM)的集成,这种内存技术提供了远高于传统DDR内存的带宽,非常适合需要大量数据处理的应用,如人工智能和图形处理。

减小封装尺寸:通过3D堆叠技术,CoWoS可以在较小的封装尺寸内实现更多的功能和更高的性能,有助于减小电子设备的体积。

提升热管理效率:CoWoS封装允许更有效地分布和散热,有助于在高性能计算中维持稳定的温度,避免过热导致的性能下降或损坏。

支持异构集成:CoWoS技术可以集成不同工艺节点的芯片,实现异构集成,这对于整合先进和成熟工艺的芯片非常有用,可以优化成本和性能。

CoWoS 工艺流程

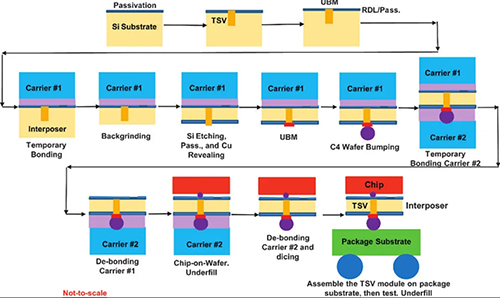

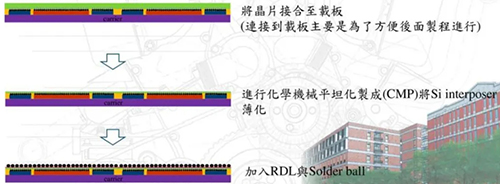

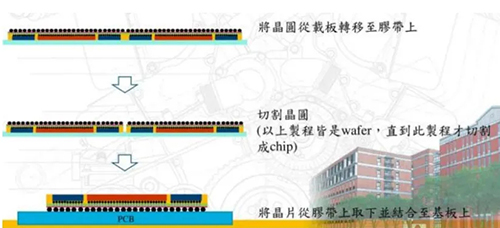

CoWoS 工艺流程包含多项步骤,根据中国台湾大学资料,总结CoWoS 封装流程可大致划分为三个阶段。在第一阶段,将裸片(Die)与中介层(Interposer)借由微凸块(uBump)进行连接,并通过底部填充(Underfill)。

在第二阶段,将裸片(Die)与载板(Carrier)相连接。封装基板(载板)是一类用于承载芯片的线路板,属于 PCB 的一个技术分支,也是核心的半导体封测材料,具有高密度、高精度、高性能、小型化及轻薄化的特点,可为芯片提供支撑、散热和保护的作用,同时也可为芯片与 PCB 母板之间提供电气连接及物理支撑。在裸片与载板相连接后,利用化学抛光技术(CMP)将中介层进行薄化,此步骤目的在于移除中介层凹陷部分。

在第三阶段,切割晶圆形成芯片,并将芯片连结至封装基板。最后加上保护封装的环形框和盖板,使用热介面金属(TIM)填补与盖板接合时所产生的空隙。

CoWoS 技术的变体

目前正在使用的 CoWoS 技术有三类:

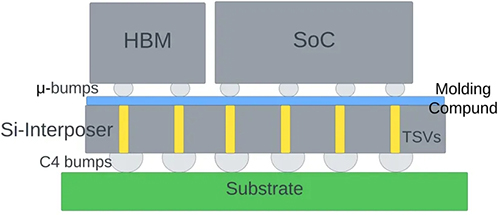

CoWoS-S:该技术使用单片硅中介层和硅通孔 (TSV),以促进芯片和基板之间高速电信号的直接传输。然而,单片硅中介层存在良率问题。

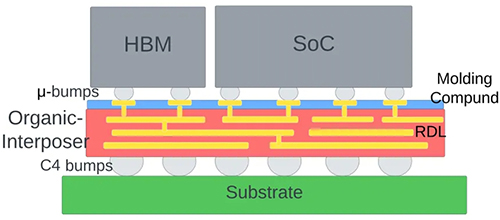

CoWoS-S 封装CoWoS-R:该技术用有机中介层取代了 CoWoS-S 的硅中介层。有机中介层具有细间距 RDL,可在 HBM 和芯片之间甚至芯片和基板之间提供高速连接。与 CoWoS-S 相比,CoWoS-R 提供了卓越的可靠性和良率,因为有机中介层本身具有柔韧性,可充当应力缓冲器,并减轻由于基板和中介层之间的热膨胀系数不匹配而引起的可靠性问题。

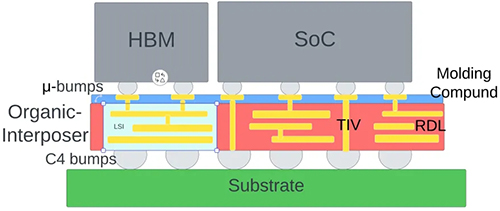

CoWoS-R 封装CoWoS-L:它使用局部硅互连 (LSI) 和 RDL 中介层一起形成重组中介层 (RI)。除了 RDL 中介层之外,它还以硅通孔 (TSV) 的形式保留了 CoWoS-S 的吸引力。这还可以缓解由于在 CoWoS-S 中使用大型硅中介层而产生的产量问题。在一些实现中,它还可以使用绝缘体通孔 (TIV) 代替 TSV 来最大限度地减少插入损耗。

CoWoS 技术的应用

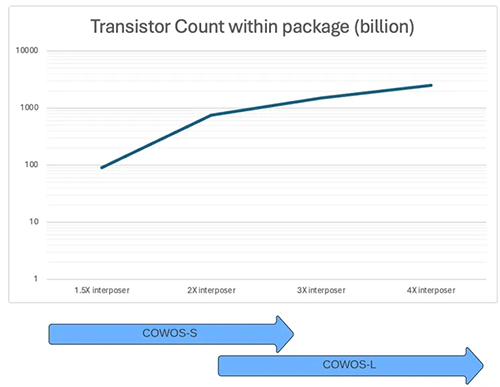

与系统级芯片 (SiP) 等旧式封装技术相比,CoWoS 技术可以在一个封装中支持更多数量的晶体管。所有需要大量并行计算、处理大量数据向量以及需要高内存带宽的应用程序都最适合使用此技术。

随着 CoWoS 的发展,晶体管数量增加CoWoS 封装技术应用广泛,目前主要应用于高性能计算、通信网络、图像处理以及汽车电子等相关领域。在高性能计算领域,CoWoS 封装具备整合多个处理器芯片、高速缓存和内存于同一封装中的能力,从而实现卓越的计算性能和数据吞吐量,这一特性在数据中心、超级计算机和人工智能应用领域具有突出的重要性,目前 CoWoS 产品聚焦于具备 HBM 记忆模块的高端产品。

许多公司因 CoWoS 封装的成功而蓬勃发展。以下是一些示例:

NVIDIA 的 AI 芯片依赖 CoWoS 封装。

AMD 也在探索将 CoWoS 封装应用于其 AI 芯片。

联发科已与台积电合作,将 CoWoS 用于其网络 ASIC。

博通 (Broadcom) 采用 CoWoS-L 作为其 ASIC 以满足深度学习和网络应用的需求。

Global Unichip Corp. (GUC) 还与台积电合作,将 CoWoS 用于其 AI、HPC 和网络应用芯片。

挑战与限制

制造复杂性和成本考虑:CoWoS 是一种 2.5D/3D 集成技术,与前代技术相比,制造复杂性显著增加。制造复杂性直接导致采用这种封装技术的芯片成本增加。这被认为是近年来 HPC 和 AI 芯片成本增加的一个重要原因。测试 CoWoS 的成本也会增加总成本。

集成和良率挑战:2.5D 和 3D 集成电路需要像任何其他集成电路一样进行测试,以确保它们没有任何制造缺陷。然而,测试 2.5D 或 3D 集成电路要困难得多,因为每个晶圆芯片在安装到中介层之前都需要单独测试,安装后还需要再次测试。除此之外,硅通孔 (TSV) 也需要测试。最后,大型硅中介层特别容易受到制造缺陷的影响,并可能导致产量损失。

散热挑战:由于中介层和基板之间的热膨胀系数 (CTE) 不同,CoWoS 封装会遇到散热问题。使用有机中介层确实可以在一定程度上限制散热问题。使用底部填充材料可以缓冲硅片和基板之间的热失配,从而大大提高焊点的寿命。

同样,在正面,重分布层 (RDL) 的完整性(尤其是两个硅片下方的重分布层)容易受到应力影响。μ-bump 底部填充材料再次充当了硅片和 RDL 之间的应力缓冲层。

电气挑战:CoWoS 封装面临着信号和电源完整性问题等电气挑战。

(1)信号完整性:逻辑晶圆到基板的互连:随着数据速率的提高,由于 TSV 的寄生电容和电感,互连的信号传输会变差。为了解决这个问题,努力优化 TSV,以最大限度地降低电容和电感。逻辑晶圆芯片到 HBM:SoC 和 HBM 之间互连的眼图性能瓶颈归因于互连的寄生电阻和电容。

(2)电源完整性:CoWoS 封装通常用于具有较高数据切换率和较低工作电压的高性能应用。这使得这些封装容易受到电源完整性挑战。

CoWoS 技术提供更高水平的集成,使集成电路能够扩展以满足不断增长的计算能力的需求。该技术不断发展,以确保更好的良率、强大的功率和热完整性,并进一步增加中介层面积,以允许更多晶圆共享同一基板。CoWoS 将在未来几年继续推动半导体行业的发展。

文章来源:半导体封装工程师之家

联系人:袁经理

手机:051683539599

电话:051683539599

邮箱:ziyu.yuan@ae-fab.com

地址: 徐高新康宁路1号高科金汇大厦A座14楼