2.2 多芯片封装

2.2.1 2.5D/3D封装:多层芯片堆叠,AI驱动下HBM需求大增,CoWoS产能成为算力关键卡口

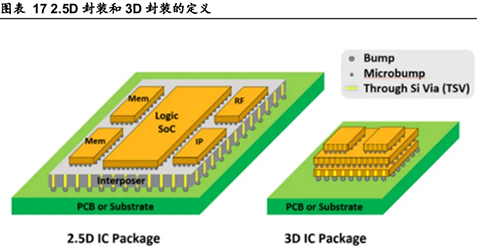

2.5D封装和3D封装的区别在于是否有硅中阶层(Si Interposer)。在2.5D封装中,所有芯片和被动元器件均在基板平面上方,至少有部分芯片和被动元器件安装在中介层上,中介层通常作为一个载体,承载着各种电路组件和接口。而3D封装舍弃中介层,直接在芯片上打孔和布线,电气连接上下层芯片。所有芯片和被动元器件器件均位于基板平面上方,芯片堆叠在一起,在基板平面的上方有穿过芯片的硅通孔(TSV),在基板平面的下方有基板的布线和过孔。

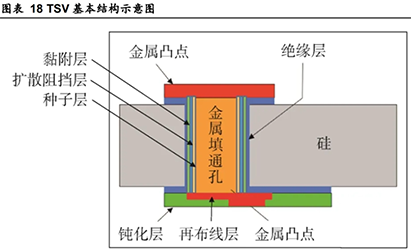

2.5D/3D封装的关键工艺是硅通孔技术(through silicon via, TSV)。TSV是一种垂直互连技术,其概念由威廉·肖克利于1958年首次提出,是指连接硅晶圆两面并与硅衬底以及其他通孔绝缘的电互连结构。TSV的尺寸通常在10μm×100μm和30μm×200μm之间,开口率介于0.1%~1%。与传统平面互连相比,TSV能够缩短互连长度、减小信号延迟、降低寄生电容和电感,实现芯片间低功耗和高速通信,同时增加宽带并实现封装的小型化。TSV目前主要应用于芯片三维堆叠、硅转接板等领域。硅转接板是芯片和有机基板的中间层,分为无源和有源两类,其中无源转接板仅包含金属互连层,而有源转接板则可集成供电、片内网络通信等功能。

根据TSV被制作的时间顺序,有3种类型的TSV工艺。分为先通孔工艺(Via First)、中通孔工艺(Via Middle)和后通孔工艺(Via Last),分别指TSV制作在晶圆制作工艺中的前、中或后段。

Via First是指在器件(如MOSFET器件)结构制造之前,先进行TSV结构的通孔刻蚀,孔内沉积高温电介质(热氧沉积或化学气相沉积),然后填充掺杂的多晶硅。多余的多晶硅通过CMP去除。

Via Middle常常指在形成器件之后但在制造叠层之前制造的通孔工艺。在有源器件制程之后形成TSV结构,然后内部沉积电介质。淀积阻挡层钛金属和铜种子层,然后电镀铜填充通孔,或通过化学气相沉积钨金属填充通孔。

Via Last包括两种工艺。正面后通孔工艺是在Back End of Line(BEOL)工艺处理结束后,从晶圆正面形成通孔的一种制造工艺。从概念上讲,在晶圆上制造的后通孔工艺与中通孔工艺相似,但是对工艺温度有进一步的限制(必须小于400℃)。背面后通孔工艺是在BEOL工艺处理结束后,从晶圆背面进行通孔结构的一种制造工艺。首先使用粘合剂将两个器件晶圆以面对面方式粘合,接下来,将顶部晶圆减薄,将TSV结构刻蚀至顶部晶圆和底部晶圆上的焊盘,孔内沉积电介质,最后,将金属沉积到TSV结构中并进行表面金属层再布线。

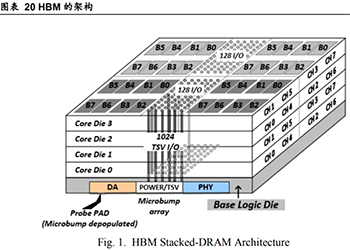

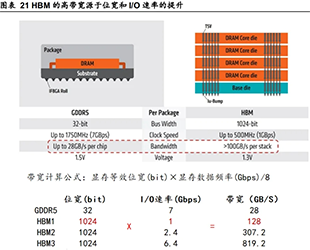

HBM使用2.5D/3D封装技术打破“内存墙”制约,成为AI及高性能计算需求下的主流方案。高带宽内存(High Bandwidth Memory, HBM)通过逻辑芯片和多层的DRAM堆叠来实现高速数据传输,突破了带宽瓶颈,成为AI训练芯片的首选。第一代HBM的架构如下图所示,由4层DRAM和逻辑芯片堆叠在一起,每层之间通过TSV和微凸点连接。每个HBM有8个通道,每个通道有128个I/O,因此每个HBM有1024个I/O,即合计1024个TSV位于HBM的中间区域。存储器和处理器通过无源转接板上的再布线层(RDL)将HBM逻辑芯片的端口物理层(Port Physical Layer, PHY)与处理器的PHY相连。HBM的性能较传统GDDR5更具优势,GDDR5的带宽最高可达32 GB/s,而HBM1、HBM2和HBM2的带宽分别达到了128 GB/s、307 GB/s和819 GB/s。其中,HBM内部的DRAM堆叠属于3D封装,而HBM与芯片其他部分合封于硅中介层上属于2.5D封装。

HBM的带宽提升源于堆栈式封装带来的高位宽以及I/O速率的提升。1)位宽:HBM的位宽是GDDR5的32倍。显存带宽是指显示芯片与显存之间的数据传输速率,带宽的计算公式为:显存带宽(GB/s) = 显存实际频率(MHz) × 显存数据倍率 × 显存等效位宽(bit) / 8。GDDR5的频率可达1750 MHz,采用4倍速率机制,其等效频率为7000 MHz,但GDDR5内部I/O位宽仅32 bit;相比之下,HBM的频率为500 MHz,采用2倍速率机制,等效频率为1000 MHz,但HBM内部I/O位宽高达1024 bit,将带宽提升至128 GB/s。HBM之所以能实现32倍于GDDR5的I/O位宽,是因为它采用了堆栈式设计,通过TSV堆栈方式将DRAM裸片垂直堆叠放置,从而实现在相同底面积上布置了数倍的DRAM颗粒,以达到更高的I/O数量。2)I/O速率:在数值上,显存速率和显存频率是相等的,使带宽计算公式简化为:显存带宽(GB/s) = 显存数据速率(Gbps) × 显存等效位宽(bit) / 8。这是因为显存速率表示每秒传输的数据位数,单位为bps (bits per second)。显存频率以MHz为单位,频率单位赫兹的本质就是,描述了单位时间内完成周期性变化的次数。因此,在数值上,显存速率和显存频率是相等的。根据JEDEC固态技术协会发布的HBM3标准,HBM3定义高达6.4 Gb/s的数据速率,堆栈中的DRAM芯片数量(四到十六个)及其具体容量(每堆栈4 GB到64 GB)不等,计算得到初始HBM3堆栈可提供每堆栈819GB/s的传输带宽。

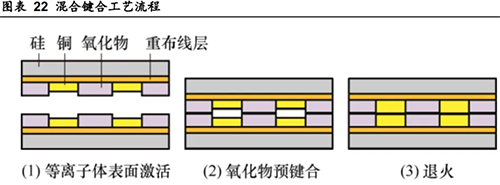

HBM堆栈层数增加对芯片间键合技术提出更高的要求,关键改进是使用混合键合替代原来的微凸点键合。混合键合是一种实现介质层与介质层、金属与金属界面无缝隙键合的技术,芯片键合界面由介质层(通常为SiO2)和金属(通常为Cu)组成。SiO2介质层为集成单元提供机械支撑与电气隔离,Cu-Cu键合提供芯片间的垂直电气互连。对于Cu和SiO2混合键合结构,首先要对键合表面进行等离子或快速原子束表面激活处理,之后进行直接键合,最后进行退火处理。退火在增强SiO2-SiO2键合强度的同时,也促进了Cu晶粒的生长和扩散以实现Cu-Cu键合。海力士计划将混合键合技术应用于下一代HBM4产品,混合键合技术可以大幅缩小电极尺寸,从而实现更高的I/O密度,同时可以显著缩小芯片之间的间隙,减少产品厚度。

混合键合的主要优点包括:1)缩小互联间距:它可以实现超细间距的芯片互连,比传统微凸点连接提高了10倍以上。超细间距的连线将增加布线的有效使用面积,增加通道数量,并实现数据处理串并行转换,简化I/O端口电路,增大数据传输带宽。2)降低信号延时:它可以实现芯片之间的无凸点互连通信,取消微凸点连接,进一步降低通道的寄生电感性和信号延时。3)减薄芯片厚度:混合键合可以实现超薄芯片的制备,通过芯片的减薄可以大幅降低芯片的厚度和重量,并进一步提升互连带宽;4)提高键合可靠性:混合键合还可以提高键合的可靠性,通过分子尺度的铜-铜触点融合和二氧化硅-二氧化硅的分子共价键连接,大幅提高了界面键合力,增强了芯片对环境的适应性。

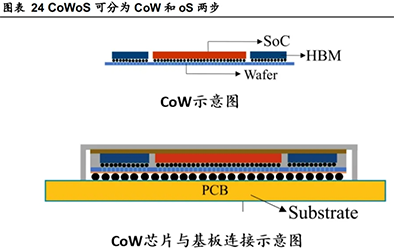

HBM的高密度连接和短互联间距,要求台积电的CoWoS封装技术。CoWoS是台积电于2012年研发的一种2.5D集成封装技术,可分为CoW和oS两步,CoW(chip on wafer)是将计算核心、I/O die、HBM等芯片封装在硅中介层上;然后再把CoW芯片整体封装在基板(Substrate)上,即oS(on substrate)环节。CoWoS可以节省空间,实现HBM所需的高互联密度和短距离连接;还能将不同制程的芯片封装在一起,在满足AI、GPU等加速运算的需求的同时控制成本。目前所有先进的AI计算芯片都使用HBM,而几乎所有HBM都封装在CoWoS上。

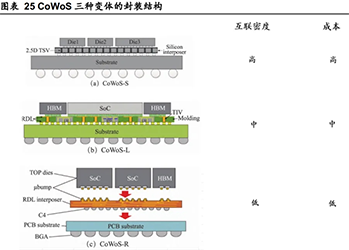

根据中介层材料的不同,CoWoS有三种变体:CoWoS-S(中介层是Si衬底)、CoWoS-R(中介层由RDL构成)和CoWoS-L(中介层由Chiplet和RDL组成),其中CoWoS-S为量产主要配置。CoWoS-S利用硅片作为桥梁,芯片互联密度最高;出于成本的考虑,CoWoS-R采用有机转接板,但也导致芯片互联密度较低;CoWoS-L将小硅桥安装在有机转接板中,仅在芯片链接部分使用硅片,实现邻近芯片边缘的高密度连接,生产成本和性能介于CoWoS-R和CoWoS-S之间。

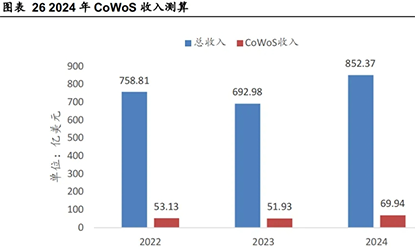

2024年,CoWoS预计为台积电带来70亿美元营收。AI需求驱动下,CoWoS在台积电营收的比重逐渐上升。根据Information Network估计,2022/2023/2024年CoWoS收入占台积电营收的比例将分别达到7.00%/7.49%/8.21%。以台积电2024年全年营收指引852.37亿美元估算,AI将带来约69.94亿美元的CoWoS营收,较2023年同比增长34.69%。

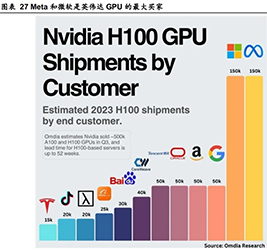

CoWoS的绝大多数需求来自AI。英伟达的H100、A100均由台积电代工,并使用CoWoS先进封装。根据Omdia,2023Q3英伟达售出近50万个A100和H100 GPU,Meta和微软是最大买家,其次是谷歌、亚马逊、甲骨文和腾讯。得益于人工智能和高性能计算的需求,本财年第三季度,Nvidia在数据中心硬件上获得了145亿美元的收入。庞大的需求量导致CoWoS产能供不应求。除了英伟达外,AMD的最新AI GPU产品MI300也导入台积电的CoWoS(2.5D)和SoIC(3D)的技术。此外,还有一系列ASIC芯片,如英特尔的Habana Gaudi、谷歌的TPU v5e、亚马逊的Inferentia和Trainium芯片等。

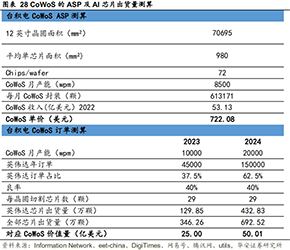

根据我们的测算,CoWoS封装的单价为722.08美元/颗,2023年/2024年基于CoWoS的芯片出货量将达到346万颗/693万颗,其中供给英伟达的芯片分别为130万颗/433万颗。按照12英寸晶圆面积70695 mm²和H100、A100、Epic Genoa、MI300四种AI芯片平均面积980mm²,测算得到每张晶圆上芯片数约72颗。根据Information Network给出的2022年CoWoS月产能为8500片以及前文测算的2022年台积电CoWoS收入,得到单颗芯片CoWoS封装价格约为722.08美元。而根据DigiTimes的报道,2023年CoWoS年产能约12万片,2024年将冲上24万片,其中英伟达将取得14.4-15万片。由于这些芯片多在7nm和5nm节点生产,保守假设良率为40%。我们以英伟达2023年和2024年分别取得4.5万片和15万片的产能来算,预计英伟达出货量约130万颗和433万颗。全体AI芯片出货量约346万颗和693万颗,对应2023年/2024年CoWoS将产生25亿美元/50亿美元收入。

供需短缺情况将在13个月内得到缓解,非台积供应链(non TSMC)有机会受益。台积电已于2023年第二季度开始采取行动扩产,包括将部分InFO产能从龙潭转移至南科,以便在龙潭转扩CoWoS产能。2023年7月25日,台积电宣布拟投资900亿新台币(约206亿元人民币)于竹科辖下铜锣科学园区新建先进封装厂,以加速扩产CoWoS产能,预计2026年底建厂完成,2027年开始量产。此外,台积电同时也将部分委外至其他封测厂,联电、安靠、矽品等均提供产能支持。影响CoWoS扩产的关键是设备交货时间较长。台积电董事长刘德音在2023年9月6日出席大师论坛专题演讲会时称,CoWoS预期1年半后可100%满足客户需求。因此对非台积供应链来说,在CoW端接单的窗口期已不足13个月,加之扩产时间考虑,各封测厂商对于扩产态度与规模较为保守。

2.2.2 系统级封装(SiP):多个子芯片集成,良率更高

系统级封装(System In Package, Sip)是指将多个子芯片集成在一个封装中,从而实现一个基本完整的功能的封装方式。传统的摩尔定律主要关注处理器和存储器的技术发展趋势,而这些器件可能只占据整个系统中器件数目的10%。除此之外,系统中还包括电源、天线、过滤器、传感器、驱动电路、转换电路、开关、电阻和电容等。如果试图将这些技术集成在单一芯片中,可能会导致性能不佳。因此,业界正在积极开发SiP(系统级封装)等封装技术,以实现更好的性能和集成。

SiP封装技术介于SoC芯片和chiplet封装之间。系统级芯片SoC(System on a Chip)将不同功能元器件整合在单个芯片,开发时间长、良率低,且各功能模块的纳米制程必须相同。系统级封装SiP(System in a Package)将多芯片异构集成,开发时间较短、良率较高,部分可重复使用。单独IP集成Chiplet将一类满足特定功能的小芯粒通过die-to-die内部互联,各功能模块的纳米制程可以不同。

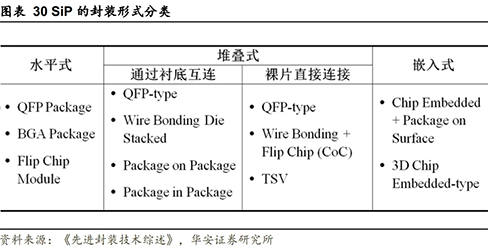

SiP可以采用水平式、堆叠式或嵌入式的封装方式。从结构上看,SiP可以分为三类,一类是2D封装结构,其中多个芯片水平排列在基板上,这种结构的封装面积较大,封装效率较低,但是工艺相对简单和稳定。另一类是堆叠封装,其中芯片垂直叠放,这种结构可以实现高效的封装,充分发挥SiP的技术优势,3D SiP的实现需要多种先进的封装工艺,如芯片堆叠(CoC)、硅通孔(TSV)等,以确保整个系统的可靠性和性能。还有一类是嵌入式封装,需要使用埋入式基底(Embedded Subtrate)技术。

2.2.3 芯粒(Chiplet):多颗小芯粒灵活组装,支持异构集成

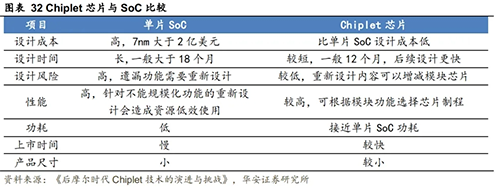

Chiplet将芯片划分为小芯粒,具备灵活性和功能性优势。Chiplet对需要实现的复杂功能进行分解,然后开发出多种具有单一特定功能的裸芯片,这些来自不同功能、不同工艺节点的裸芯片可相互进行模块化组装,最终形成一个完整的芯片。这种方法实现了异质集成,为芯片设计带来了更大的灵活性和可扩展性,有效提升了产品的功能性。当前,Chiplet架构主要应用于服务器处理器芯片、人工智能加速芯片、通信芯片、移动与桌面处理器芯片和晶圆级处理器芯片。

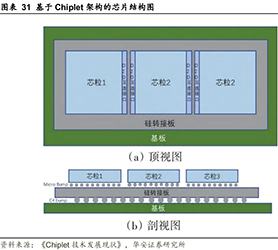

在Chiplet架构中,芯粒之间通过互连接口实现电气连接。下图展示了基于Chiplet架构的芯片,该芯片包含三种不同功能的芯粒。这些芯粒通过D2D互连接口进行电气互连,同时通过硅转接板和基板进行物理连接。芯粒与硅转接板之间通过micro bump互连,以支持芯粒间高速信号的高密度互连。硅转接板与底部基板之间则通过C4 bump实现互连,用于传递电源和外部I/O等功能。

Chiplet具备良率、成本、异构计算优势,适用于复杂功能的定制化需求。由于Chiplet由多颗芯粒组成,单颗芯粒的面积较小,其良率高。直接设计一整块SoC的面积较大,可能导致较低的良率,从而带来高昂的成本。此外,Chiplet技术支持封装内部的异构集成,可以根据模块功能选择芯片制程,针对特定功能模块设计专用的高性能芯片,对于其他通用芯片粒采用成熟制程。

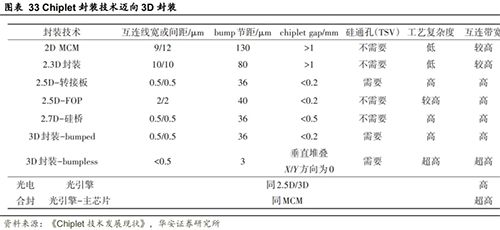

Chiplet封装技术也正迈向3D封装,互联节距持续缩小。Chiplet封装广泛使用各类先进封装技术,包括2D MCM、2.3D封装、2.5D-转接板、2.5D-FOP、2.7D-硅桥、3D封装-bumped、3D封装-bumpless等。封装结构已从2D封装发展到3D封装,互联间距从12μm缩短至0.5μm以下,bump节距从过去的130μm缩小至3μm。互连带宽逐步增加,互连质量逐步提升。

3. 先进封装市场

3.1 市场规模:受下游旺盛需求拉动,先进封装增速高于传统封装

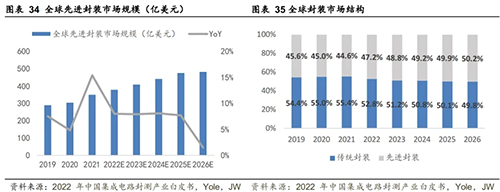

AI及高性能计算需求旺盛,先进封装景气度高于整体封装行业。根据JW Insights和Yole,全球先进封装市场规模有望从2022年378亿美元上升至2026年482亿美元,CAGR约为6.26%。从全球封装市场结构来看,2022年先进封装的市场份额为47.2%。由于先进封装市场增速超过传统分装市场增速,先进封装的市场份额将持续提升,预计至2026年将达到50.2%。

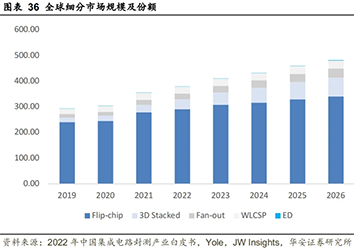

目前先进封装仍然以倒片封装为主,3D堆叠和ED增速较快。根据JW Insights和Yole,Flip-chip是市场规模最大的先进封装工艺,2022年市场规模达到290.94亿美元,占比76.7%,其后为3D堆叠(38.33亿美元)、Fan-out(22.05亿美元)、WLCSP(26.98亿美元)、ED(0.78亿美元)。在各先进封装工艺中,成长性较高的是3D堆叠和ED。3D堆叠封装2022年市场规模为38.33亿美元,预计2026年可以达到73.67亿美元,2022年-2026年CAGR为18%,主要是受高性能运算、AI等领域的需要拉动。嵌入式基板封装(ED)是一种先进的封装技术,在5G硬件和CIS等场景有较大的增量空间。2022年ED的市场规模为0.78亿美元,预计2026年可以达到1.89亿美元,2022年-2026年CAGR为25%。

3.2 竞争格局:海外IDM和Foundry掌握先进封装前沿技术

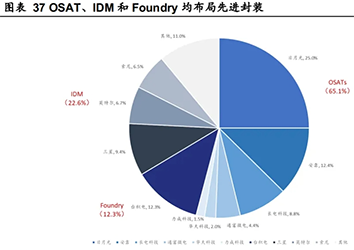

IDM(集成电路制造商)和Foundry(晶圆代工厂)开拓高端3D封装,而OSAT(外包封测公司)主攻中低端倒装、晶圆级封装。根据Yole,2022年集成电路先进封装市场中,OSATs的市场份额为65.1%,IDM的市场份额为22.6%,Foundry的市场份额为12.3%。先进封装头部六位玩家市场份额超70%,包括3所外包封测公司日月光(占比25.0%)、安靠(占比12.4%)、长电科技(占比8.8%),1所晶圆代工厂台积电(占比12.3%)以及2所集成电路制造商三星(占比9.4%)、英特尔(占比6.7%)。

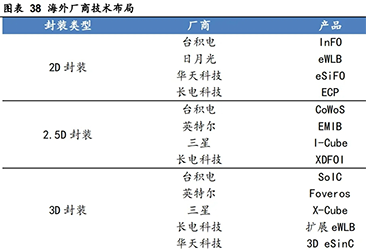

先进封装向2.5D/3D进发,技术路线由海外Foundry和IDM厂主导。台积电已成为先进封装技术创新的引领者之一,相继推出了基板上晶圆上的芯片(Chip on Wafer on Substrate, CoWoS)封装、整合扇出型(Integrated Fan-Out, InFO)封装、系统整合芯片(System on Integrated Chips, SoIC)等;英特尔推出了嵌入式多芯片互连桥接(Embedded Multi-Die Interconnect Bridge,EMIB)、三维逻辑芯片封装(Foveros)等先进封装技术;三星推出了I-Cube(Interposer-Cube)、X-Cube(eXtended-Cube)技术。

文章来源:半导体封装工程师之家

联系人:袁经理

手机:051683539599

电话:051683539599

邮箱:ziyu.yuan@ae-fab.com

地址: 徐高新康宁路1号高科金汇大厦A座14楼