在以人工智能、高性能计算为代表的新需求驱动下,先进封装应运而生,发展趋势是小型化、高集成度,历经直插型封装、表面贴装、面积阵列封装、2.5D/3D封装和异构集成四个发展阶段。

典型封装技术包括:

1)倒片封装(Flip-Chip):芯片倒置,舍弃金属引线,利用凸块连接;

2)扇入型/扇出型封装(Fan-In/Fan-Out):在晶圆上进行整体封装,成本更低,关键工艺为重新布线(RDL);

3)2.5D/3D封装:2.5D封装中芯片位于硅中介层上,3D封装舍弃中介层,进行多芯片堆叠,在基板上方有穿过芯片的硅通孔(TSV);

4)SiP封装:将多个子芯片异构集成,缩短开发时间、提高良率;

5)Chiplet:多颗具有单一特定功能的小芯粒异构组装,具备成本优势。

全球先进封装市场规模有望从2022年378亿美元上升至2026年482亿美元,CAGR约为6.26%。其中,3D堆叠CAGR高达18%,市场规模有望在2026年上升至73.67亿美元。先进封装头部六位玩家市场份额超70%,技术路线由台积电、英特尔、三星等海外领先Foundry和IDM厂主导。

1. 封装行业现状与发展趋势

1.1 先进封装属于中道工艺,涉及部分前道工艺与设备

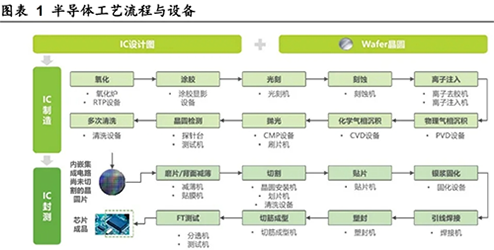

半导体工艺流程包括前道晶圆制造工序和后道封装测试工序。前道工序是晶圆制造工序。在前道工序中,晶圆经历了氧化、涂胶、光刻、刻蚀、离子注入、物理/化学气相沉积、抛光、晶圆检测、清洗等一系列步骤,每一步都需要相应的半导体制造设备。后道工序是封装测试工序。在后道工序中,尚未切割的晶圆片进入IC封测环节,经历磨片/背面减薄、切割、贴片、银浆固化、引线焊接、塑封、切筋成型、FT 测试,每一环节同样需要相应的半导体封装设备与半导体测试设备。最终得到芯片成品。

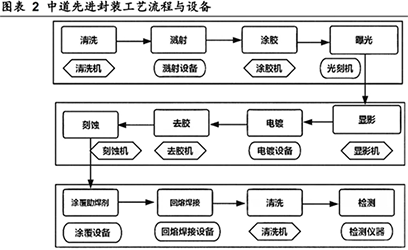

传统封装已不能满足以人工智能、高性能计算为代表的新需求,先进封装技术应运而生,形成独特的中道工艺。先进封装也称为高密度封装,具有引脚数量较多、芯片系统较小和高集成化的特点。先进封装属于中道工序,包括清洗、溅射、涂胶、曝光、显影、电镀、去胶、刻蚀、涂覆助焊、回炉焊接、清洗、检测等一系列步骤。与传统的后道封装测试工艺不同,先进封装的关键工艺需要在前道平台上完成,是前道工序的延伸。

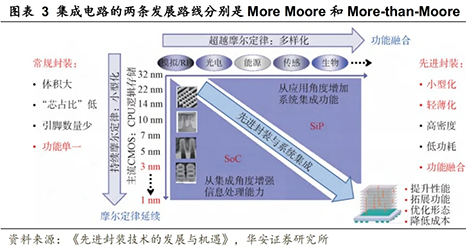

1.2 后摩尔时代,先进封装打破“存储墙”与“面积墙”

集成电路沿着两条技术路线发展,分别是More Moore和More-than-Moore。More Moore代表持续追随摩尔定律,致力于推动先进制程的发展。这一路线的关键策略是通过不断微缩互补金属氧化物半导体(Complementary Metal-Oxide-Semiconductor, CMOS)器件的晶体管栅极尺寸,以增加芯片晶体管数量,从而提升芯片性能。目前,量产芯片的工艺制程已发展至3 nm节点。全球范围内仅有少数企业,如台积电、英特尔和三星,具备10纳米及以下节点的制造能力。与More Moore相对应的是More-than-Moore,这一趋势旨在超越摩尔定律,将发展方向引向多样化。More-than-Moore采用先进封装技术,在一个系统内集成处理、模拟/射频、光电、能源、传感、生物等多种功能,从而实现了系统性能的全面提升。相对于传统封装方式,先进封装具有小型化、轻薄化、高密度、低功耗和功能融合等诸多优势,能够提升性能、拓展功能、优化形态、降低成本。

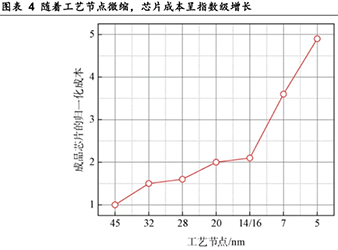

推进摩尔定律成本高昂,先进封装能够在不缩小制程节点的背景下,仅通过改进封装方式就能提升芯片性能。摩尔定律是指集成电路上可容纳的晶体管数目,约每隔18-24个月便会增加一倍,器件性能也将提升一倍。近年来,摩尔定律的尺寸微缩趋势放缓,先进制程已经逼近物理极限,通过迈向更先进的制程提升芯片性能的成本呈指数级增长。如下图所示,相比于采用45nm节点制造的250平方毫米芯片,采用16nm工艺节点后,每平方毫米的成本增加了1倍以上;而采用5nm工艺后,成本将增加4~5倍。与此同时,先进封装仍处于相对高成本效益的阶段。根据Semi,晶圆制造的设备投资占比超过80%,而封装测试的设备投资占比不到20%。尽管先进封装同样需要使用光刻、刻蚀、沉积等设备,但相较于晶圆制造,先进封装所需的设备的精度要求低,其设备价值也相对较低。此外,先进封装技术目前正处于快速发展阶段,未来有较高的改进和降本空间。

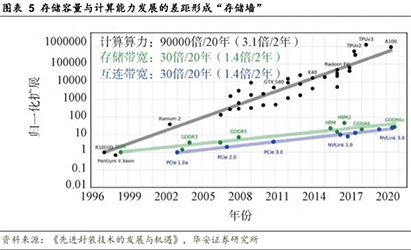

“存储墙”制约算力性能发挥,先进封装实现近存计算和高带宽内存堆叠,提高传输效率。处理器的峰值算力每两年增长约3.1倍,而动态存储器的带宽每两年增长约1.4倍。存储器的发展速度远远落后于处理器,两者之间的差距达到1.7倍。此外,日益增长的带宽需求量也是一个重要瓶颈。数据的爆发式增长对网络信息的传输速度和容量提出了更高的要求。在过去的几十年中,串行通信的速度从1Gb/s增长到100Gb/s,并行通信的速度从1Tb/s增长至100Tb/s。现有计算平台的架构基于冯·诺依曼的“存算分离”,使得数据需要频繁在存储单元和数据单元间搬移。为了解决“存储墙”,业界提出了存内计算和近存计算两种方法。存内计算是指在存储单元中嵌入计算单元,实现数据的实时计算,这种计算方式可以大大减少数据搬运,降低能耗,提高计算效率。近存计算则基于2.5D/3D先进封装技术,实现存储单元和计算单元的距离的缩短和多个高带宽内存的堆叠,高效地传输数据。

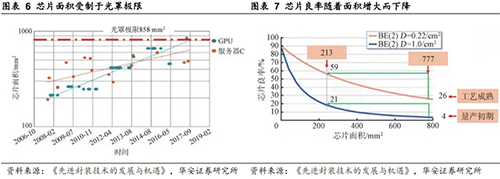

集成电路发展受到“面积墙”挑战,先进封装Chiplet集成多个小芯粒凸显良率优势。扩大芯片面积可以实现更多晶体管的集成,从而提高芯片性能。然而,光刻机的光罩限制了芯片的尺寸,目前最先进的极紫外光刻机的最大光罩面积为858 mm²(26 mm×33 mm)。2020年,英伟达发布A100 GPU芯片,采用台积电7 nm工艺,制造了近似于一个光罩面积的芯片,面积为826 mm²(~25.5 mm×32.4 mm),具有540亿个晶体管,逼近芯片面积极限。此外,随着芯片尺寸的增大,芯片的良率逐渐下降。在工艺成熟的情况下,当芯片面积从213 mm²增至777 mm²时,良率从59%降低至26%,良率的降低将使芯片的成本变得高昂。而先进封装Chiplet能将大尺寸的SoC芯片按功能拆分为一个个小芯粒,主要功能采用先进制程,次要功能采用成熟制程,再通过封装技术集成,在采用小芯片的同时实现相近的性能。

1.3 封装技术持续迭代,发展趋势是小型化、高集成度

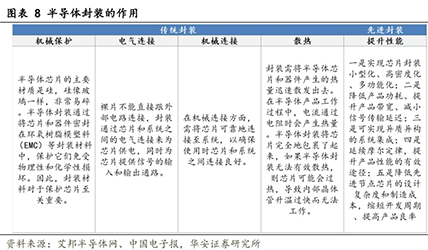

传统封装的主要作用包括机械保护、电气连接、机械连接和散热。1)机械保护:裸片易碎,容易受到物理性和化学性损坏。半导体封装的主要作用是通过将芯片和器件密封在环氧树脂模塑料(EMC)等封装材料中,保护它们免受物理性和化学性损坏。2)电气连接:裸片不能直接跟外部电路连接,封装通过芯片和系统之间的电气连接来为芯片供电,同时为芯片提供信号的输入和输出通路。3)机械连接:需将芯片可靠地连接至系统,以确保使用时芯片和系统之间连接良好。4)散热:封装需将半导体芯片和器件产生的热量迅速散发出去。在半导体产品工作过程中,电流通过电阻时会产生热量。半导体封装将芯片完全地包裹了起来,如果半导体封装无法有效散热,则芯片可能会过热,导致内部晶体管升温过快而无法工作。

先进封装在封装的四大功能的基础上,还肩负着提升芯片性能的作用。具体而言,先进封装对芯片的提升作用包括五个方面:一是实现芯片封装小型化、高密度化、多功能化;二是降低产品功耗、提升产品带宽、减小信号传输延迟;三是可实现异质异构的系统集成;四是延续摩尔定律,提升产品性能的有效途径;五是降低先进节点芯片的设计复杂度和制造成本,缩短开发周期、提高产品良率。

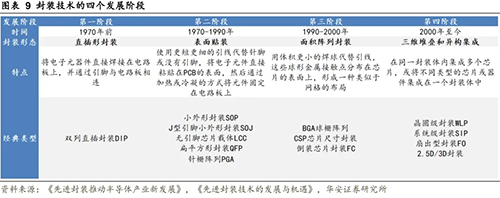

封装技术的发展趋势是小型化、高集成度,可分为四个阶段:1)第一阶段(1970年前):直插型封装,特点是将电子元器件直接焊接在电路板上,并通过引脚与电路板相连,以双列直插封装DIP(Dual In-line Package)为主;2)第二阶段(1970-1990年):表面贴装,其特点是使用更短更细的引线代替针脚或没有引脚,将电子元件直接粘贴在PCB的表面,然后通过加热或冷凝的方式将元件固定在电路板上。主要包括小外形封装SOP(Small Outline Package)、J型引脚小外形封装SOJ(Small Outline J-leaded)、无引脚芯片载体LCC(Leadless Chip Carrier)、扁平方形封装QFP(Quad Flat Package)四大封装技术和针栅阵列PGA(Pin Grid Array)等技术;3)第三阶段(1990-2000年):面积阵列封装,特点是用体积更小的焊球代替引线,这些球形金属接触点分布在芯片的表面上,形成一种类似于网格的布局。包括BGA球栅阵列(Ball Grid Array)、CSP芯片尺寸封装(Chip Scale Package)、倒装芯片封装FC(Flip-Chip)等先进封装技术;4)第四阶段(2000年至今):三维堆叠和异构集成,晶圆级封装WLP(Wafer Level Package)、系统级封装SIP(System In Package)、扇出型封装FO(Fan-Out)、2.5D/3D封装等先进封装技术百花齐放。总结来看,每一代封装技术的本质区别是芯片与电路连接方式的区别,随着封装技术的发展,实现了连接密度和传输速率不断提高。

2. 典型封装技术

2.1 单芯片封装

2.1.1 倒片封装(Flip-Chip):芯片倒置,利用凸块连接

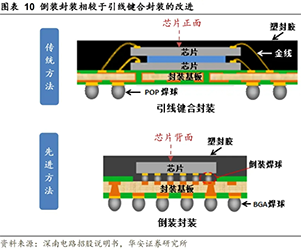

倒片封装舍弃金属引线,利用凸块(bumping)连接。传统的引线键合方法采用细金属线进行连接,通过热、压力和超声波能量,将金属引线与芯片焊盘以及基板焊盘牢固焊接,实现了芯片与基板之间的电气互连和芯片之间的信息传递。这一过程中,金属引线在焊接的过程中起到了关键作用,通过引线实现了有效的电连接。引线键合广泛应用于射频模块、存储芯片以及微机电系统器件封装。而倒装封装舍弃引线,在芯片顶侧形成焊球,然后将芯片翻转贴到对应的外部电路的基板上,利用加热熔融的焊球实现芯片与基板焊盘结合。这种封装技术通常被广泛应用于高性能处理器(如CPU和GPU)、芯片组(Chipset)以及其他要求高密度互连和紧凑尺寸的集成电路封装。倒片封装与引线键合在工艺的不同之处在于:

1)倒片封装将芯片倒置,芯片正面倒扣在基板上;2)倒片封装舍弃金属引线,利用凸块连接,需要进行凸块键合。

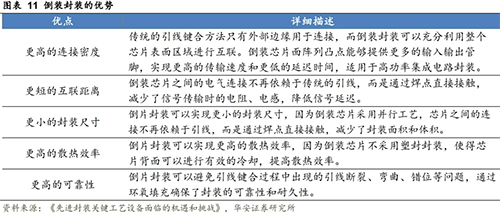

与传统的引线键合相比,倒装芯片具备众多优势:

1)更高的连接密度:传统的引线键合方法只有外部边缘用于连接,而倒装封装可以充分利用整个芯片表面区域进行互联。倒装芯片面阵列凸点能够提供更多的输入输出管脚,实现更高的传输速度和更低的延迟时间,适用于高功率集成电路封装。

2)更短的互联距离:倒装芯片之间的电气连接不再依赖于传统的引线,而是通过焊点直接接触,减少了信号传输时的电阻、电感,降低信号延迟。

3)更小的封装尺寸:倒片封装可以实现更小的封装尺寸,因为倒装芯片采用并行工艺,芯片之间的连接不再依赖于引线,而是通过焊点直接接触,减少了封装面积和体积。

4)更高的散热效率:倒片封装可以实现更高的散热效率,因为倒装芯片不采用塑封封装,使得芯片背面可以进行有效的冷却,提高散热效率。

5)更高的可靠性:倒片封装可以避免引线键合过程中出现的引线断裂、弯曲、错位等问题,通过环氧填充确保了封装的可靠性和耐久性。

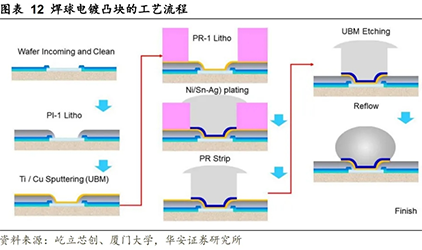

倒片封装的关键工艺是Bumping。凸块是定向生长于芯片表面,与芯片焊盘直接相连或间接相连的具有金属导电特性的凸起物,按材质可分为金凸块、焊球凸块、铜柱凸块。主流的凸块工艺均采用圆片级加工,即在整片圆片表面的所有芯片上加工制作凸块,常用方式有蒸发方式、印刷方式和电镀方式。焊球电镀凸块的工艺流程为:首先,采用溅射或其它物理气相沉积的方式在圆片表面沉积一层Ti/Cu作为电镀所需种子层;其次,在圆片表面旋涂一定厚度的光刻胶,并运用光刻曝光工艺形成所需要图形;然后,圆片进入电镀机,通过控制电镀电流、时间等,从光刻胶开窗图形的底部开始生长并得到一定厚度的金属层作为UBM;最后,通过去除多余光刻胶、UBMEtching及回流工艺实现电镀凸块制作。

2.1.2 扇入型/扇出型封装(Fan-In/Fan-Out):在晶圆上进行整体封装,成本更低

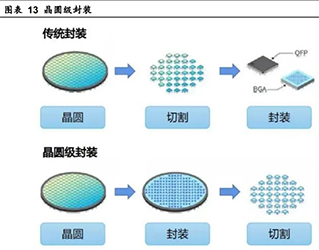

晶圆级封装(Wafer-Level Packaging, WLP)是一种直接在晶圆上完成封装的技术。晶圆级封装与传统封装的区别在于,传统封装先将成品晶圆切割成单个芯片再封装;晶圆级封装在芯片还在晶圆上时就进行整体封装,封装完成再进行切割分片。晶圆级封装具备以下优点:1)成本更低:晶圆级封装的成本相对较低,因为批次性处理方式使得成品晶圆能够一次性全部封装。

2)体积更小:晶圆级封装把整个芯片作为一个整体进行封装,此外,晶圆级封装通常采用无引脚或极少引脚的形式,进一步减小封装体积。

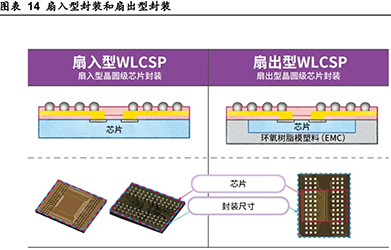

晶圆级封装可分为两大类型:扇入型WLCSP(Fan-In Wafer Level Chip Scale Package, Fan-In WLCSP)和扇出型WLCSP(Fan-Out Wafer Level Chip Scale Package, Fan-Out WLCSP)。在扇入型WLCSP中,封装尺寸与芯片本身尺寸相同,封装布线、绝缘层和锡球直接位于晶圆顶部。扇出型WLCSP在封装后的尺寸大于芯片本身尺寸,是指先对晶圆进行切割再封装,切割好的芯片排列在载体上,芯片与芯片之间的空隙用环氧树脂模塑料填充,重塑成晶圆。然后,这些晶圆将从载体中取出,进行晶圆级处理,并被切割成扇出型WLCSP单元。

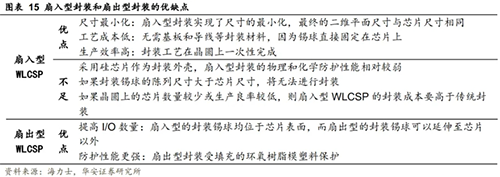

扇入型WLCSP具备如下优点:1)尺寸最小化:扇入型封装实现了尺寸的最小化,最终的二维平面尺寸与芯片尺寸相同;2)工艺成本低:无需基板和导线等封装材料,因为锡球直接固定在芯片上;3)生产效率高:封装工艺在晶圆上一次性完成。但扇入型WLCSP也存在一些局限。由于采用硅芯片作为封装外壳,扇入型封装的物理和化学防护性能相对较弱。在封装尺寸上,如果封装锡球的陈列尺寸大于芯片尺寸,将无法进行封装。此外,如果晶圆上的芯片数量较少或生产良率较低,则扇入型WLCSP的封装成本要高于传统封装。扇入型封装常用于低I/O数量(一般小于400)和较小裸片尺寸的工艺中。

扇出型WLCSP是对扇入型封装的改进,具备如下优点:1)提高I/O数量:扇入型的封装锡球均位于芯片表面,而扇出型的封装锡球可以延伸至芯片以外。2)防护性能更强:扇出型封装受填充的环氧树脂模塑料保护。

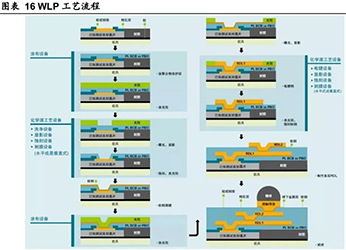

WLP工艺流程的关键工艺为重新布线(RDL)。首先,涂覆第一层聚合物薄膜,以加强芯片的钝化层,起到应力缓冲的作用。聚合物种类有光敏聚酰亚胺(PI)、苯并环丁烯(BCB)、聚苯并恶唑(PBO)。其次,重布线层(RDL),对芯片的铝/铜焊区位置重新布局,使新焊区满足对焊料球最小间距的要求,并使新焊区按照阵列排布。光刻胶作为选择性电镀的模板以规划RDL的线路图形,湿法蚀刻去除光刻胶和溅射层。然后,涂覆第二层聚合物薄膜,使圆片表面平坦化并保护RDL层。在第二层聚合物薄膜光刻出新焊区位置。随后,凸点下金属层(UBM),采用和RDL一样的工艺流程制作。最后,为植球步骤,焊膏和焊料球通过掩膜板进行准确定位,将焊料球放置于UBM上,放入回流炉中,焊料经回流融化与UBM形成良好的浸润结合,达到良好的焊接效果。

文章来源:半导体封装工程师之家

联系人:袁经理

手机:051683539599

电话:051683539599

邮箱:ziyu.yuan@ae-fab.com

地址: 徐高新康宁路1号高科金汇大厦A座14楼