在之前,有人曾表示,混合键合将成为自 EUV 以来半导体制造最具变革性的创新。事实上,它将对设计流程产生比 EUV 本身更大的影响,从封装架构延伸到单元设计和布局。知识产权生态系统将发生巨大重塑,制造流程也将发生巨大重塑。2D 晶体管缩小的时代仍将继续,但步伐缓慢,但混合键合将带来芯片设计者思考 3D 的新时代。

但semianalysis却表示,随着这句充满炒作的谣言结束,我们应该注意到,将混合键合技术大规模推向市场存在许多重大的工程和技术挑战,因为如今它仅保留给少数 AMD 芯片、CMOS 图像传感器和一些供应商的 3D 芯片和NAND。这种转变将重塑供应变化和设计流程。

半导体行业观察之前的文章《混合键合,成为“芯”宠》中,就介绍了这个技术。在这里,我们编译了semianalysis的科普文章,带大家进一步了解这个技术。

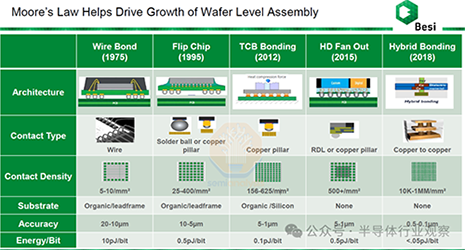

在封装史上,最后一次重大范式转变是从引线键合到倒装芯片。从那时起,更先进的封装形式(例如晶圆级扇出和 TCB)一直是相同核心原理的渐进式改进。这些封装方法都使用某种带焊料的凸块作为硅与封装或板之间的互连。这些技术可以一直缩小到约 20 微米的间距。

到目前为止,我们在多部分先进封装系列中讨论的主要封装类型和工艺流程已达到 220 微米到 100 微米规模,并且主要使用焊料作为各种小芯片铜互连之间的介质。为了进一步扩展,需要另一种范式转变:采用混合键合的无凸块互连。混合键合的尺寸超出了 10 微米互连间距,路线图为 100 纳米范围,并且它不使用任何中介物(intermediary),例如具有更高电阻的焊料。

相反,不同芯片或晶圆的互连直接通过铜通孔连接。直接铜连接可以降低电阻,从而在向各种芯片发送数据时降低功耗。当与连接数量的数量级增加相结合时,需要对设计进行彻底的重新思考。

在介绍混合键合之前,我们再看一下先进封装的全部意义是什么?我们可以看到,封装技术的进步旨在实现更大的互连密度(每个区域有更多的互连),减少迹线长度(trace length )以降低每比特传输的延迟和能量。我们可以看到混合键合如何解决这两个问题:迹线长度显显著缩短,因此延迟尽可能低,无需on-die,并且在某些情况下比芯片上的global rounding更短,并且互连间距可以远低于 10 微米以增加密度。

混合键合到底是什么?

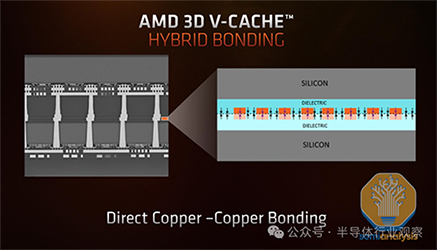

混合键合用于芯片的垂直(或 3D)堆叠。混合键合的显著特点是它是无凸块的。它从基于焊料的凸块技术转向直接铜对铜连接。这意味着顶部die和底部die彼此齐平。两个芯片都没有凸块,而是只有可缩放至超细间距的铜焊盘。没有焊料,因此避免了与焊料相关的问题。

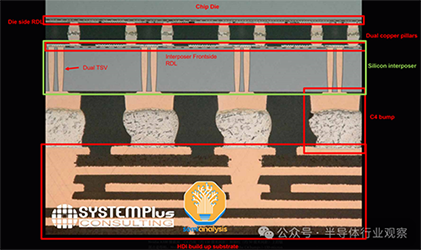

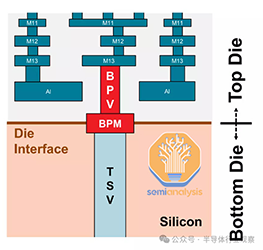

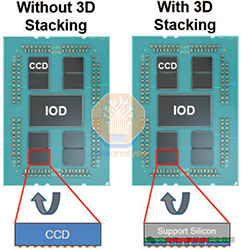

从上图中,我们可以看到AMD 3D V-Cache的横截面,它采用台积电的SoIC-X的die-to-wafer混合键合。顶部和底部硅之间的键合界面是混合键合层,存在于硅芯片(silicon dies)的金属层的顶部。混合键合层是一种电介质(现在最常见的是 SiO 或 SiCN),采用通常为亚 10 微米间距的铜焊盘和通孔进行图案化。

电介质的作用是使每个焊盘绝缘,使得焊盘之间不存在信号干扰。铜焊盘通过硅通孔 (TSV) 连接到芯片金属层。TSV 需要向堆栈中的其他芯片传输电源和信号。当底部芯片“面朝下”(face down)放置时,需要这些通孔来连接顶部芯片上的金属层,穿过晶体管层到达底部芯片上的金属层。

信号正是通过这些铜焊盘进行芯片间通信。这种键合之所以是“混合”键合,是因为它是电介质-电介质键合(dielectric-dielectric bond)和直接铜对铜键合(direct copper-to-copper bond)的组合。键合界面之间没有使用额外的粘合剂或材料。

关键工艺条件

与以前的基于凸块的互连相比,引入了一系列全新的技术和工艺挑战。为了实现高质量的键合,对表面光滑度、清洁度和粘合对准精度有非常严格的要求。我们将首先描述其中一些挑战,因为流程是围绕缓解这些挑战而设计的。记住这些将帮助您更好地理解为什么流程是这样的,以及不同方法的优缺点。

颗粒和清洁度

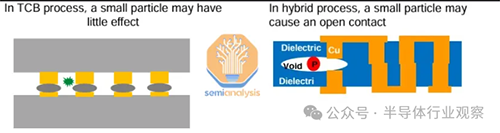

在任何有关混合键合的讨论中,都会提到颗粒(Particles)。这是因为颗粒是混合键合中良率的敌人。由于混合键合涉及将两个非常光滑且平坦的表面齐平地键合在一起,因此键合界面对任何颗粒的存在都非常敏感。

高度仅为 1 微米的颗粒会导致直径为 10 毫米的粘合空隙,从而导致键合缺陷。对于基于凸块的互连,器件和基板之间始终存在间隙,因为使用了底部填充或非导电薄膜,因此可以容纳一些颗粒。

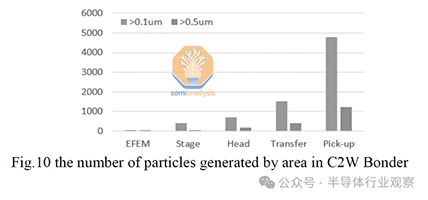

保持清洁至关重要,而且非常具有挑战性。颗粒来自晶圆切割、研磨和抛光等许多步骤。任何类型的摩擦都会产生颗粒,这是一个问题,特别是因为混合键合涉及机械拾取芯片并将其放置在其他芯片的顶部。工具中存在大量来自芯片键合头和芯片翻转器的运动。颗粒是不可避免的,但有几种技术可以减轻对良率的影响。

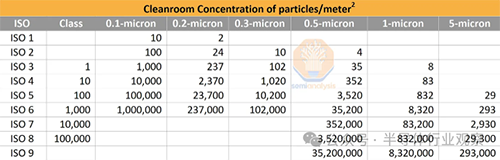

当然,定期进行晶圆清洗以去除污染物。然而,清洁是不完美的,并且不能一次性去除 100% 的污染物,因此最好首先避免污染物。混合键合所需的洁净室比其他形式的先进封装所需的洁净室要先进得多。

因此,混合键合一般需要1级/ISO 3级或更好的洁净室和设备。例如,台积电和英特尔正在一路迈向 ISO 2 或 ISO 1 级别。这是混合键合被视为“前端”工艺的一个主要原因,即它发生在类似于晶圆厂的环境中,而不是传统封装厂商 (OSAT) 的环境中。鉴于清洁度要求的升级,OSAT 很难追求混合键合。如果大多数 OSAT 想要参与混合键合,则需要建造更新、更先进的洁净室,而台积电和英特尔等公司可以使用较旧的晶圆厂或按照与现有晶圆厂类似的标准进行建设。

混合键合的工艺流程还涉及许多传统上仅由晶圆厂专用的工具。ASE 和 Amkor 等外包组装和测试公司 (OSAT) 在化学气相沉积 (CVD)、蚀刻、物理气相沉积 (PVD)、电化学沉积 (ECD)、化学机械平坦化 (CMP) 和表面处理方面经验相对较少准备/激活。

清洁度要求和工具增加相结合导致成本大幅增加。与其他形式的封装相比,混合粘合工艺并不便宜。我们将在下面介绍整个流程。

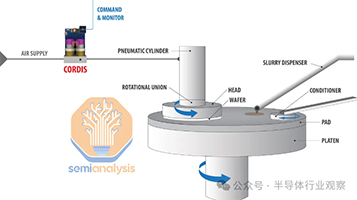

光滑度

混合键合层的表面光滑度也极其关键。HB 界面同样对任何类型的形貌都敏感,这会产生空洞和无效的键合。一般认为电介质的表面粗糙度阈值是 0.5nm,铜焊盘的表面粗糙度阈值是 1nm。为了达到这种平滑度,需要执行化学机械平坦化 (CMP),这对于混合键合来说是非常关键的工艺。

抛光后,需要在整个流动过程中始终保持这种光滑度。避免任何可能损坏该表面的步骤,例如严厉的清洁。即使是用于晶圆分类的探测也需要进行调整,以免表面受到损坏。

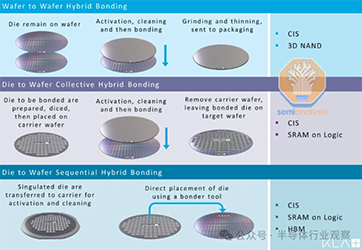

晶圆到晶圆(W2W)或芯片到晶圆(D2W)

首先讨论W2W(Wafer-to-Wafer )还是D2W(Die-to-Wafer)。混合键合可以通过晶圆到晶圆 (W2W) 或芯片到晶圆 (D2W) 工艺来完成。W2W 意味着两个制造好的晶圆直接键合在一起。W2W 提供更高的对准精度、吞吐量和键合良率。鉴于 W2W 相对容易,目前绝大多数混合绑定都是通过 W2W 完成的。

W2W键合良率更高的原因在于对准和键合步骤是分开的。在 W2W 工具中,有一个单独的腔室(chamber)来执行对齐。一旦顶部和底部晶圆对齐,它们就会被移入键合室(bonding chamber,处于真空中),在那里用一点力将它们压在一起,大约 20 分钟后,形成初始预键合。

W2W 的关键在于它是一个更加干净的过程,步骤更少。在对准和键合之前,可以清洁晶圆以去除大部分颗粒。芯片分割是颗粒污染的一个来源,仅发生在键合之后。由于它是晶圆级工艺,因此还可以为对准步骤提供更多的时间,因此较长的对准时间不会像芯片级工艺那样损害良率。

腔室内也没有发生太多运动,因此腔室内本身的污染物较少。目前,W2W键合机可以实现50nm以下的对准精度。W2W键合已经是一个成熟的工艺并且不是特别昂贵。证据是我们看到它广泛应用于大众市场产品,如 3 层图像传感器和 NAND。

W2W 键合效果很好,但一个主要限制是无法执行晶圆分类来选择已知良好的芯片 (KGD)。这会导致将有缺陷的芯片粘合到良好的芯片上,从而导致良好硅的浪费。

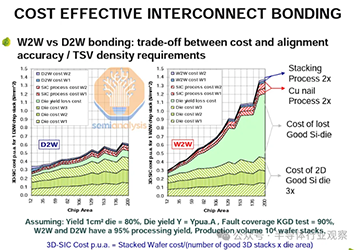

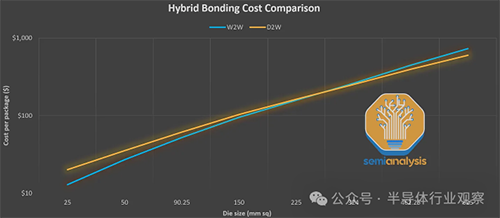

鉴于此,W2W 用于良率高的晶圆,这通常意味着较小的设计。在下图中我们可以看到W2W和D2W的芯片面积和成本之间的关系。在较小的芯片尺寸上,W2W 更便宜,因为晶圆产量会更高。然而,当我们采用更大的芯片尺寸时,W2W 成本曲线变得更加陡峭,这主要是由丢失的好芯片的成本驱动的。随着芯片尺寸的增大,每个晶圆上的良好芯片部分会减少,从而导致有缺陷的芯片和良好芯片的接合更多。

我们可以看到,W2W 用于具有高产量的较小芯片:CMOS 图像传感器、3D NAND,并且在逻辑方面到目前为止仅用于Graphcore 的Bow IPU。

虽然 Graphcore Bow IPU 是一款较大的 HPC 芯片,但顶部芯片不是前沿逻辑,而是用于电力传输的无源电容器芯片,因此其良率应该相当高,并且硅片要便宜得多。W2W 的另一个缺点是顶部芯片和底部芯片的尺寸必须一致,因此这限制了异构集成选项的灵活性。

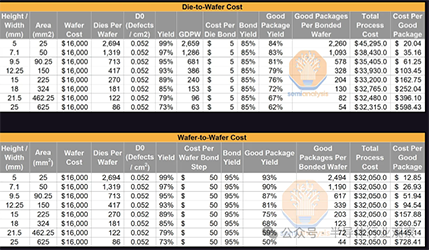

关于成本有多种杠杆。主要是晶圆成本、D0(缺陷密度)和建和良率。这些杠杆中的每一个都可能导致更高或更低的成本。请注意,这些是强调这一点的示例图。不要使用下面的图表,因为它没有显示实际的键合成本。

可以看出,D2W 在小芯片上更昂贵,但在大芯片上,情况就相反了。W2W 更贵。仅测试和键合已知良好芯片 (KGD) 的能力至关重要,这也是晶圆芯片 (D2W) 率先实现产品化的原因,而不是冒着缺陷堆积和浪费优质硅的风险。它可以应对较差的良率,但仍然具有商业上可行的产品。

为了克服限制,我们需要使用 D2W。D2W 键合更具挑战性。执行晶圆分类后,KGD 从顶部晶圆上分离出来,并通过拾放工具单独附着到基础晶圆上。这在键合方面更具挑战性,因为每个晶圆有更多的键合步骤。这些额外的步骤会引入更多的颗粒污染,尤其是来自芯片分割和拾放期间键合头的移动的颗粒污染。

D2W 可以是一个“collective”工艺,其中 KGD 对齐并首先临时粘合到重构的载体晶圆上。然后将重构的载体晶圆键合到基础晶圆上以进行实际的预键合。这是为了像 W2W 一样将对准和粘合分开,并允许在最终预粘合、、键合之前进行清洁步骤,以清除已积累的任何污染物。缺点是涉及额外的步骤,并且额外的 W2W 键合步骤会产生更多的对准错误机会。

这实际上是一个简单的流程,因为底部芯片也可以在载体晶圆上重构。因此,顶部和底部芯片都是从原始硅晶圆上切割而成,并且对 KGD 进行分类。两组芯片都粘合到各自载体上的精确位置上。然后,通过 W2W 工艺粘合 2 个承载晶圆。这是在台积电 SOIC 中完成的。因此,每个 AMD 3D V 缓存芯片(底部 CPU 芯片到载体、3D V 缓存小芯片到载体、2x 虚拟硅到载体)和晶圆上晶圆都使用 5 个键合步骤。

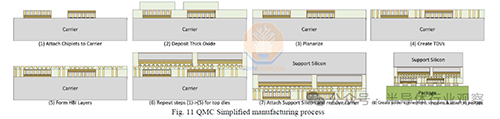

重构的流程还可以用于异构集成的更极端的选择。英特尔在 IEDM 2022 上展示了“准单片芯片 (QMC:quasi-monolithic chips)”应用的一个例子是一个封装,顶部和底部各有 2 个芯片的异构集成。对于顶部和底部,每个芯片都连接到载体晶圆上。然后用厚的无机氧化物(例如SiO2)对晶圆进行模制。W2W 键合已完成。然后模制的芯片被分割并附着到封装基板上以完成流程。

请注意,重构区域中可能存在 TSV。

直接 D2W (Direct D2W)键合是将单个芯片直接放置到目标晶圆上进行预接合。Direct D2W 还不太成熟,但由于流程简化,未来似乎会更多地使用直接 D2W。集体 D2W(collective D2W ) 的好处之一是可以执行清洁,然后直接发送到对准室以减少污染。最近推出的 D2W 集群工具可以重新创建此流程,从而减少此集体流程的好处。此外,D2W 更适合更精细的焊盘间距,因为对准变得更具挑战性,因此消除 W2W 步骤是有好处的,这会在 W2W 步骤中引入额外的未对准风险。

鉴于 D2W 混合键合的工艺挑战和成本,当前的应用受到限制。AMD 是 2022 年的第一个采用者,并且迄今为止仍然是唯一的采用者。

需要注意的一件事是,W2W 在对准方面远远领先于 D2W,因此,如果您的设计不是异构的,并且晶圆良率足够高,那么它实际上将是一种更准确、更高良率的工艺。这种更精细的间距还将解锁许多 D2W 尚未进入的新用例。

文章来源:半导体行业观察编译自semianalysis

联系人:袁经理

手机:051683539599

电话:051683539599

邮箱:ziyu.yuan@ae-fab.com

地址: 徐高新康宁路1号高科金汇大厦A座14楼