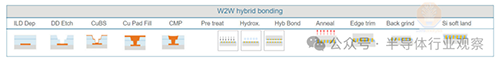

混合键合工艺流程

接下来让我们更详细地了解 D2W 和 W2W 的流程。

TSV形成

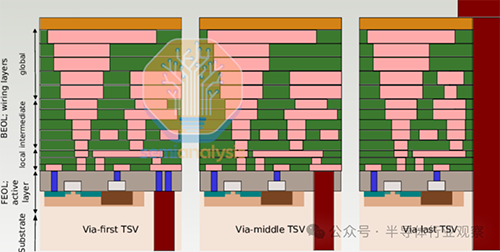

正如我们上面提到的,需要 TSV 来向封装中的所有芯片传输电源和信号。想象一下传统的倒装芯片封装。该芯片仅需要一侧互连即可接收电力并与封装基板进行数据通信。该互连层具有连接到无源布线层(也称为“金属层”或“线路后端”/BEOL)的凸块,无源布线层为开关和处理数据的晶体管层提供电源和信号。

对于 3DIC,底部的芯片需要能够与其下方的封装基板以及顶部的芯片进行通信,因此芯片的两侧都需要互连。这就是 TSV 的用武之地。TSV 有多种变体,具体取决于它们在流程中的制造时间。TSV 可以是“先通孔”(即先在晶体管层之前在硅中制造),也可以是“中间通孔”(即在晶体管层完成之后且在金属层之前制造),或者是BEOL 之后繁荣“后通孔”(即先在晶体管层之前制造)。

3DIC 最常见的是“中间通孔”方法,因为 TSV 在金属层之间运行,一直延伸到晶体管层,并在芯片背面显露出来,因此芯片的两侧现在都有一层互连我们将对此进行描述。

晶圆上涂有光刻胶,然后使用光刻法进行图案化。然后,使用深反应离子蚀刻 (DRIE:Deep Reactive Ion Etch) 将 TSV 蚀刻到硅中,以在晶圆深处形成高深宽比沟槽,但这不会穿过整个晶圆。使用化学气相沉积 (CVD) 沉积绝缘层(SiOX、SiNx)和阻挡层(Ti 或 Ta)。这些层是为了防止铜扩散到硅中。然后,使用物理气相沉积 (PVD) 沉积铜种子层(copper seed layer)。该种子层沉积在沟槽中,然后使用电化学沉积 (ECD) 进行填充。这形成了 TSV。然而,该过程尚未完成,因为背面尚未显露通孔。为了显露 TSV,需要对 TSV 背面进行抛光,并且在某些情况下进行蚀刻,以减薄背面并随后显露出 TSV。一旦完成,晶圆就可以继续形成 BEOL。

TSV 的形成并不简单,而且可能非常耗时,特别是由于需要深蚀刻。我们知道 TSV 形成是 HBM 和 CoWoS 生产的瓶颈。一些客户从硅中介层转向 CoWoS-R的原因之一是为了避免硅中介层中昂贵的 TSV 工艺。

混合键层形成

在晶圆的键合界面之后,混合键合层被制造在晶圆的 BEOL 顶部。无论W2W还是D2W都是一样的。这是一层带有细间距铜通孔图案的介电薄膜。电介质,通常是碳氮化硅 (SiCN),是通过 PECVD 沉积的。然后形成焊盘。使用光刻技术对铜焊盘的孔进行图案化并蚀刻掉。沉积阻挡层和种子层,然后使用典型的铜镶嵌工艺镀铜。

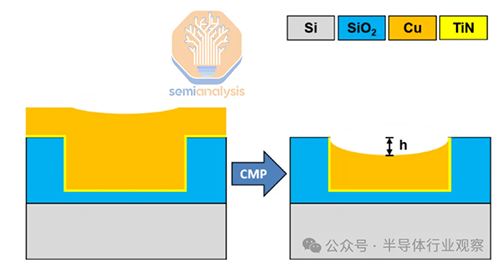

然后,进行 CMP 步骤来研磨并平滑电介质表面,并获得正确的铜轮廓。铜焊盘的一个显著特征是它们凹入约 1 微米间距。如前所述,光滑的表面对于形成良好的粘合至关重要。电介质的粗糙度必须控制在 0.5nm 以内,铜焊盘的粗糙度必须控制在 1nm 以内。

HB 接口的一个特征是铜焊盘最初凹入介电层下方约 5 纳米。这是为了确保铜在退火过程中不会妨碍初始电介质-电介质键合。如果铜凹陷得太深,则可能无法正确形成铜-铜键合。

在对铜和其他金属进行 CMP 时,由于过度抛光以及金属和电介质的柔软度不同,经常会出现凹陷现象。虽然并不理想,但这种现象并不严重,并且可以解决。需要控制凹陷的精确轮廓,以防止键合过程中铜过度/生长不足。

为了获得正确的凹陷轮廓,需要结合低和高铜去除浆料的多个 CMP 步骤。CMP 是混合键合的关键工艺,可实现非常光滑的表面和最佳轮廓。

在 ECTC 上,索尼展示了当间距降至 1 微米时,最好让铜突出而不是凹陷。

晶圆分类/分割

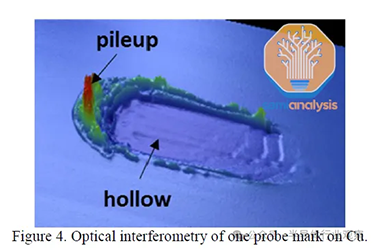

仅对于 D2W,执行晶圆分类,并对 KGD 进行分割并在载体晶圆或带框架上重组,以便可以对其进行进一步处理。如上所述,HB 给传统晶圆分类工艺带来了新的复杂性。晶圆分类涉及用探针探测晶圆凸块或焊盘以执行电气测试。

探测可能会对铜焊盘表面造成少量损坏,从而破坏 CMP 过程中表面的光滑度。虽然对焊盘的损坏很小并且在大多数情况下通常可以接受,但 HB 对少量的形貌变化更加敏感,因为这些变化会影响粘合质量。解决此问题的一种方法是在初始 CMP 中对此进行补偿,然后执行另一轮 CMP 后探测,以消除探测造成的任何损坏。

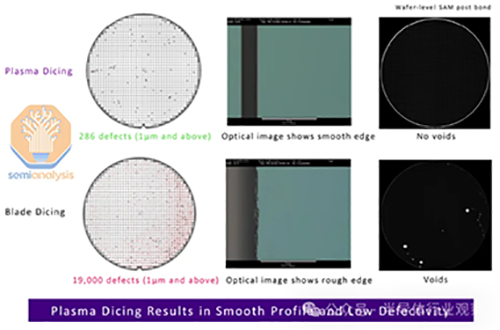

对于分割/切割,一个问题是过程中产生的颗粒。一般不使用刀片划片,因为它最脏:导致大量颗粒和大量良率损失。激光切割和等离子切割优于刀片切割,因为它们是更清洁的工艺,但仍然会产生颗粒物质。等离子切割是最极端的方法,其机制与蚀刻掉分隔芯片的划线类似。然而,考虑到蚀刻整个晶圆所需的时间,这个吞吐量要低得多。迪斯科是这方面的领导者。

一种缓解技术是首先在晶圆上涂上一层保护层。颗粒落在保护层上,当保护层被剥离时,颗粒可以与保护层一起被去除。虽然这有助于解决分割过程中的颗粒问题,但可能会留下保护层的残留物,并且剥离过程也可能对 HB 层造成一些表面损坏,从而增加表面粗糙度。

等离子激活和清洁

现在对 2 个晶圆进行处理,为粘合做好准备。它们经过 N2 等离子体处理以激活表面。等离子处理改变了表面的特性,以增加表面能并使其更加亲水。使两个表面更加亲水可以使表面促进氢键结合。这有助于在室温下实现下一步中发生的初始弱电介质-电介质预键合。

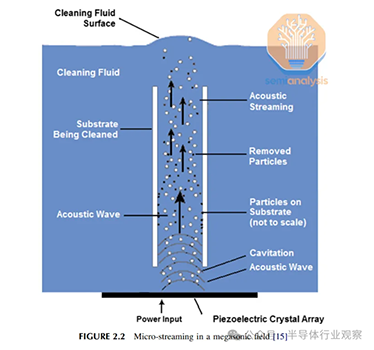

处理后,进行最终清洁以清除任何积累的颗粒。重要的是,在键合之前,传入的晶圆尽可能干净。清洁需要彻底但又不能造成损坏,以保持 HB 接口的完整性。

最好的方法似乎是在兆声波辅助下进行去离子水清洁。使用洗涤器或基于等离子的清洁可能会造成太大的破坏和/或引入污染物。

键合Bonding

现在是键合步骤。更准确地说,它更像是“预键合”,因为此步骤仅形成初始电介质-电介质键合,只是弱范德华键。我们将分别介绍 W2W 和 D2W 方法的流程。

(1)W2W键合W2W bonding

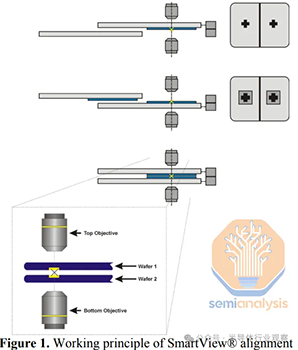

W2W键合良率更高的原因在于对准和键合步骤是分开的。首先是对齐步骤。W2W 对齐有多种技术。过去,红外扫描仪用于检查两块晶圆之间的对准情况。一个限制是一个晶圆必须对红外线透明。这不适用于 CMOS 晶圆,因为红外线无法透过金属层。

EVG 在 W2W 接合领域占据主导地位,拥有获得专利的 SmartView 对准技术。有 2 个相互校准的相机,一台放置在目标晶圆上方,一台放置在下方。移动固定顶部晶圆的卡盘,以便底部摄像头可以识别对准标记,并且系统记录对准标记的位置。顶部晶圆被缩回,然后底部晶圆在相机之间移动,直到顶部相机能够识别对准标记。对准器现在可以通过计算 2 个对准标记的相对位置来对准 2 个晶圆。为了帮助保持精度和控制,晶圆彼此非常接近(50 微米以内),并且卡盘仅在 X 和 Y 平面上移动,在预键合之前没有 Z 轴(垂直)移动。

对准后,晶圆被移入键合室,在其中施加小压力约 20 分钟将它们压在一起,形成初始键合。

键合后检查可以通过声学在原位完成,如果对准不充分,则也可以重新加工键合。

在 W2W 工具中,有一个单独的室来执行对齐。一旦顶部和底部晶圆对齐,它们就会被移入键合室(处于真空中),在那里用一点力将它们压在一起,大约 20 分钟后形成初始预键合。W2W 的关键在于它是一个更加干净的过程,步骤更少。在对准和键合之前,可以清洁晶圆以去除大部分颗粒。芯片分割是颗粒污染的一个来源,仅发生在键合之后。

由于它是晶圆级工艺,因此还可以为对准步骤提供更多的时间,因此较长的对准时间不会像芯片级工艺那样损害产量。腔室中也没有发生太多运动,因此腔室本身产生的污染物较少。目前,W2W键合机可以实现50nm以下的对准精度。W2W键合已经是一个成熟的工艺并且不是特别昂贵。证据是我们看到它广泛应用于大众市场产品,如索尼、Omnivison 和三星的图像传感器,以及长江存储、西部数据和 Kioxia 的 NAND。

(2)D2W键合D2W bonding

D2W 接合是通过拾放工具完成的。

底部目标晶圆位于晶圆卡盘上。将待粘合的芯片面朝上放置在胶带框架上。翻转臂收集单个芯片并将其翻转,使芯片的背面朝上位于翻转器上。有一个高架键合臂,可利用键合头上的真空吸力拾取翻转的芯片。

文章来源:半导体行业观察编译自semianalysis

联系人:袁经理

手机:051683539599

电话:051683539599

邮箱:ziyu.yuan@ae-fab.com

地址: 徐高新康宁路1号高科金汇大厦A座14楼